# 《计算机原理》 教 案

|        |                                         |                 |                         |    | <b>-</b> |         |      |    |   |

|--------|-----------------------------------------|-----------------|-------------------------|----|----------|---------|------|----|---|

| 学<br>科 | 计算机<br>应用                               | 课 题             | 第五章 存储系统                |    |          |         |      |    |   |

|        |                                         |                 | 5.2.3 高速缓冲存结构           |    |          |         |      | 课次 |   |

| 授课时间   |                                         | 2017年12月18日、21日 |                         |    | 课的类型     | 新授课     |      |    |   |

| 授课方法   |                                         | 讲授法、启发、指导       |                         |    |          | 授课时数    | 4    |    |   |

| 教      | . 具                                     | 多媒体、            | 、计算机组                   | 且件 | 授课班级     |         |      |    |   |

| 教      | 学目标                                     | 2. 掌握           | Cache 作<br>地址映射<br>替换策略 |    |          |         | 审批意见 |    |   |

| 教      | Cache 作用<br><b>学重点</b><br>地映射方法<br>替换策略 |                 |                         |    |          |         |      |    |   |

| 教      | 学难点                                     | 地映射方法           | <u>.</u>                |    |          |         |      |    |   |

|        |                                         | 教               | 学                       | 设  | 计        |         |      | 附  | 记 |

|        |                                         | 速度速度快           |                         |    |          | 度一般都很快, | 如    |    |   |

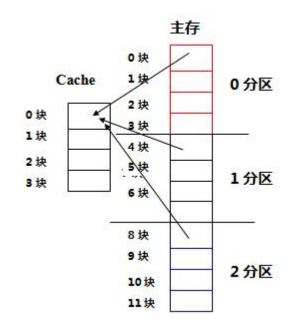

# 2017~2018 第一学期 (201709) 学 教 内 容 教师活动 学生活动 5.2.3 高速缓冲存储器 互动: 导入: 重伸位 复习上节课内 1. 高速缓冲存结构 扩展法,字扩展 高缓冲存储器是一种高速、小容量临时存储器,由 法、字位扩展法 SRAM 实现或集成到 CPU 内部。 (时间可适当 高速缓存采用 Cache-主存存储结构,如图所示: 长点,帮助学生 熟悉这些方法) 问题: 如何搭 Cache 建一价廉物美 CP 的存储器来满 IJ 足快速 CUP 需 存 要? 方法是:建立 在主存与 CPU 之间增加一个 Cache, 由于 Cache CACHE- 主存结 离 CPU 近,而且速度快,用来存储使用频繁指令和数 构 据以提高访存操作平均速度。 2. Cache 工作过程 在带有 Cache 计算机中, Cache 中开始时没有数据 或指令,当 CPU 访问主存时,从主存中读入数据或指 令同时还将数据或指令写入 Cache 中。 讲解: 以后 CPU 访问中, 若访问的数据在 Cache 中, 则直 接在 Cache 中读取,而不必访问主存,以提高访问数 据速度。 CPU 访问数据在 Cache 中情形称为命中, 反之称为不命中或失效。 3. 地址映射 在主存地址和 Cache 地址之间建立一种逻辑关系 称为地址映射。地址映射方法有:直接映射、全相映

射、组相联映射法。

(1) 直接映射

将主存按 Cache 大小分为若干个分区,分区和 Cache 再分为大小相等若干个块。

一个主存块只能映射到 Cache 指定块中。 如图所示:

0 分区、1 分区、2 分区 0 块只能映射到 Cache0 块中。

映射关系为: j=i mod cache 块数 j-cache 中块号, i-主存块号。

例:已知一个 Cache 为 2K 字,每块为 16 字,主存容量为 256K 字,试确定主存数分区数,及分区或 Cache 块数,确定主存第 129 块将映射到 Cache 第几块中?

解: 主存分区数 256K÷2K=128

一个分区或 Cache 块数: 2K÷16=2<sup>11</sup>÷2<sup>4</sup>=128 j=i mod 128 =129 mod 128 =1

主存 129 块将映射到 cache 第 1 块中。

## (2) 全相映射

主存分为 Cache 大小若干个分区,主存、Cache 分为若干大小相同分区,主存块可映射到 cache 中任意块。

全相映射优点:命中率高。

**重点:** 直接映射

画图:理解

讲解:

缺点:硬件复杂

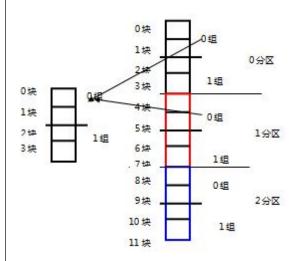

#### (3) 组相联映射

主存、cache 分成大小相等若干块,主存分成 cache 大小若干分区,分区和 cache 分成若干个大小相等组。

主存中组只能映射到 cache 指定组中,主存组中块可以映射到 cache 中对应组中任意块中。

# 4.替换策略

主存读出新块调入 Cache 中,若 Cache 中相应块已被占,此时必须用新块代替旧字块。常用替换策略有:

- (1) 先进先出策略FIF0

- (2) 近期最少使用策略LRU

讲解:

总结

- 1. 为什么要采用 Cache 结构?

- 2. Cache 地址映射方法

- 3. 替换策略有哪些?

作业

作业:

学习指导 P64 一、二、三、四、

## 2017~2018 第一学期 (201709)

| 课  | 通过学习掌握 CACHE-主存结构意义,CACHE 地址映射方法,以及替换策略。可以重 |

|----|---------------------------------------------|

| 后感 | 点提及上节课根据芯片容量计算地址和数据位数方法。                    |